XR17V352 Overview

Key Specifications

Package: LFBGA

Mount Type: Surface Mount

Pins: 113

Operating Voltage: 1.2 V

Description

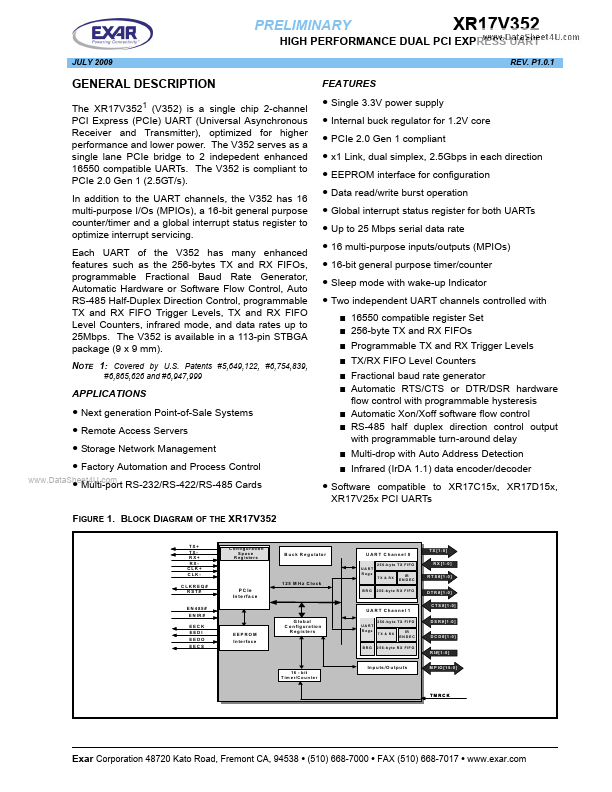

The XR17V3521 (V352) is a single chip 2-channel PCI Express (PCIe) UART (Universal Asynchronous Receiver and Transmitter), optimized for higher performance and lower power. The V352 serves as a single lane PCIe bridge to 2 indepedent enhanced 16550 compatible UARTs.

Key Features

- Single 3.3V power supply

- Internal buck regulator for 1.2V core

- PCIe 2.0 Gen 1 compliant

- x1 Link, dual simplex, 2.5Gbps in each direction

- EEPROM interface for configuration

- Data read/write burst operation

- Global interrupt status register for both UARTs

- Up to 25 Mbps serial data rate

- 16 multi-purpose inputs/outputs (MPIOs)

- 16-bit general purpose timer/counter